eZ80 never need stop

eZ80 for RC2014™ and compatible backplanes

An eZ80 CPU Module that works within the RC2014™ ecosystem

31 May 2024

I want this new eZ80 module to operate on a backplane, with an original Z80 module also. Dual CPU mode.

This will allow it to function within my Yellow MSX platform, where the standard Z80 can operate in true timing accurate backward compatible mode for games etc, and the eZ80 can be switched on specifically by applications and services to get true Super performance.

This is akin to how the MSX Turbo machines operated. They had a standard Z80 running at the 3.5Mhz for games, and a Zilog R800 for the high performance mode. The MSX BIOS code has a bit of support, built in, for this CPU switching.

The Dual CPU mode should be optional also, so that the eZ80 can be the only CPU in the backplane, if desired.

There are 2 ways I considered for this to be achieved.

- Co-ordinate the BUSREQ/BUSACK signals of both the Z80 and eZ80 , so that at any one point in time, only one processor is active.

- The eZ80 is always active, and its bus access is granted as required, through some buffers.

I went for option 2.

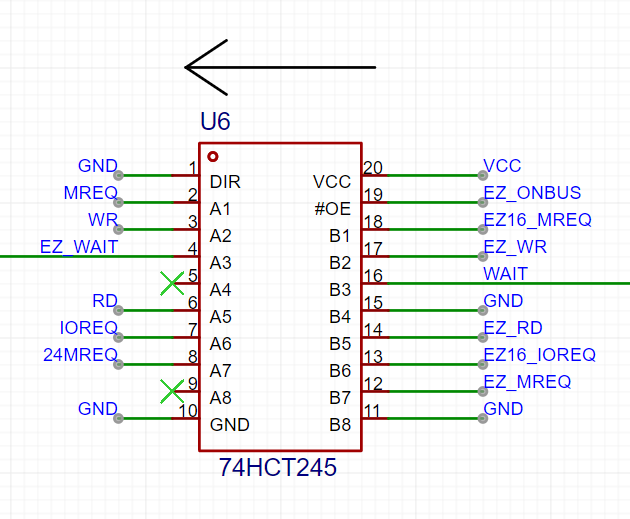

In this design, the eZ80 is isolated from the main buses via 74HCT245 buffer chips. Enough for all its address, control and data signals. The buffer chips are in 'disabled' state, when the Z80 is accessing the buses.

When its time for the eZ80 to access the bus, the Z80's BUSREQ signal is 'activated'. This will cause the Z80 to HALT, and release the bus. Once its released the bus, the Z80's BUSACK signal is activated. By connecting the BUSACK signal to the 74HCT245 buffer chip's enable signal (EZ_ONBUS), the eZ80 will only be able to access the bus, when the Z80 has fully released it.

An advantage of using these 74HCT245 buffer chips, is that they will step up the eZ80 's 3.3V signals to a good 5V signal. Although I suspect the 3.3V signal level will be 'enough' - having the higher voltage and drive would, I think, help with interfacing to lots of modules in the backplane, older modules, and generally help with signal to noise issues.

Here how I think I can make the Dual CPU mode work. (At this stage, not really sure if this will work.)

1. Z80 has the main bus access.

- The Z80's BUSREQ and BUSACK are inactive (high).

- The eZ80 's buffer chips 'Enabled' input is wired to the Z80's BUSACK.

- As such, the buffer chips are 'disabled'.

- eZ80 is unable to access the bus, except for the INT signal.

- eZ80 is operating on its internal ROM/RAM.

- eZ80 has a GPIO pin connected to the INT, configured for output.

- eZ80 can signal to the Z80 via this interrupt signal.

- The BUSACK signal is also wired to a eZ80 GPIO pin, so the eZ80 can identify if it has access to the bus.

2. The Z80's BUSREQ is activated (LOW).

- Only the Z80 can do this, by writing to a 74HC74 flip-flop, to trigger the BUSREQ signal.

3. The Z80 will be halted, as its BUSREQ is now activated (LOW).

4. The Z80 will release the address, control, and data lines.

5. The Z80 will activate its BUSACK signal (LOW).

6. The eZ80 buffer chips will become enabled.

7. The eZ80 's GPIO mapped to the BUSACK will inform the eZ80 that is now has access.

- The eZ80 could be 'interrupted' by this GPIO/BUSACK signal or it may simply be polling this pin.

- The eZ80 will change it GPIO pin mapped to the INT line from output to input.

- As the eZ80 now has access to the buses, it can, when it want to give control back to the Z80, write to the 74HC74 flip-flop to release the BUSREQ signal.